# Lec 3: Assembly

**IS561: Binary Code Analysis and Secure Software Systems**

Sang Kil Cha

# Intel (x86) Architecture

#### **x86 Instruction Set Architecture**

- 1. Introduced by *Intel* in 1978.

- 2. CISC (Complex Instruction Set Computer) architecture.

- 3. The most popular ISA.

#### History of x86 ISA

- (8086) 16-bit address space (in 1978).

- (*x86* or *IA-32*) 32-bit address space (in 1985).

- (*x86-64* or *x64* or *AMD64*) 64-bit address space (in 2003).

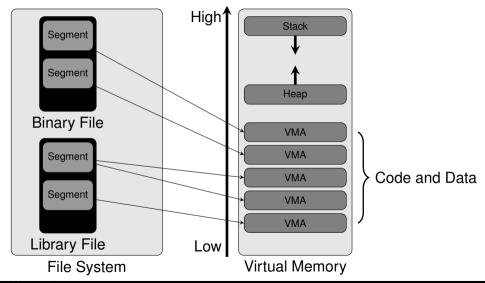

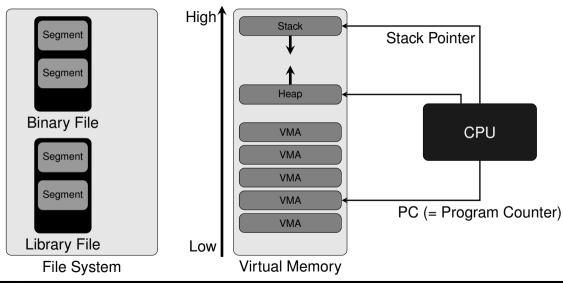

#### **Memory Layout and CPU Registers**

File System

00

#### **Memory Layout and CPU Registers**

#### **Memory Layout and CPU Registers**

#### Registers in x86 (and x86-64)

- · Stack pointers

- ESP (RSP) points to the top of the stack.

- EBP (RBP) points to the base of the current stack frame.

- Program counter (instruction pointer)

- EIP (RIP) points to the instruction to execute.

- Status register (FLAGS register)

- EFLAGS (RFLAGS) contains the current condition flags.

- Other registers

- EAX (RAX), EBX (RBX), ECX (RCX), EDX (RDX), ESI (RSI), EDI (RDI)

- x86-64 only registers: R8, R9, R10, R11, R12, R13, R14, R15

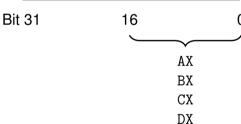

#### **Size of Registers**

- x86 registers are 32-bit. Intel says they a size of a double word.

- x86-64 registers are 64-bit. Intel says they have a size of a quad word.

#### **Double/Quad Word?**

- A word is the natural unit of data used by a processor.

- Typically, a word is 32 bits on a 32-bit machine, and 64 bits on a 64-bit machine.

- However, Intel says a word is 16 bits on both x86 and x86-64!

What's wrong?

#### **History of x86 Processors**

```

1978: 8086

16-bit processor, registers (SP, BP, IP, ...)

1982: 80286

1985: 80386

32-bit processor, registers (ESP, EBP, EIP, ...)

1989: 80486

2003: Opteron

2005: Prescott

64-bit processor, registers (RSP, RBP, RIP, ...)

2006: Core 2

```

#### **Intel x86 Convention**

- Word = 16 bits.

- Double Word (DWORD) = 32 bits.

- Quad Word (QWORD) = 64 bits.

#### x86 (32-bit) Registers

| EAX | AH | AL |

|-----|----|----|

| EBX | BH | BL |

| ECX | CH | CL |

| EDX | DH | DL |

# x86-64 (64-bit) Registers

| RAX |    |     |     | AH | AL |  |  |

|-----|----|-----|-----|----|----|--|--|

| RBX |    |     |     | BH | BL |  |  |

| RCX |    |     |     | CH | CL |  |  |

| RDX |    |     |     | DH | DL |  |  |

| Bit | 63 | 32  |     |    | (  |  |  |

|     |    |     |     |    |    |  |  |

|     |    | EAX |     |    |    |  |  |

|     |    |     | EBX |    |    |  |  |

|     |    |     | ECX |    |    |  |  |

|     |    |     | EI  | XC |    |  |  |

# x86 Memory Access = Byte Addressing

We can access data at a byte granualrity.

How do we load/store a single bit then?

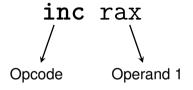

# **Assembly Basic**

# **Basic Format 1: Instructions with 2 Operands**

# **Basic Format 2: Instructions with 1 Operand**

# **Basic Format 3: Instructions with 0 Operand**

#### Two Kinds of x86 Assembly Syntax

- *Intel* Syntax: the original assembly syntax introduced by Intel.

- AT&T Syntax: used by UNIX and Linux.

We will use the Intel syntax.

## **Opcode Decides Semantics**

- mov rax, rbx

- **sub** rsp, 0x8

- inc eax

#### Addressing Modes

An addressing mode defines how a memory operand is interpreted to derive an effective address

```

register

- mov rax, [rax]

register + register

- mov rax, [rax + rbx] (= mov rax, [rax + rbx * 1])

displacement

- mov rax, [0x1000]

• register + register × scale + displacement

```

- mov rax, [rax + rbx \* 4 + 0x1000]

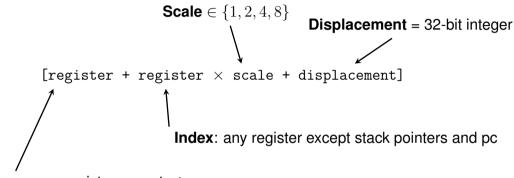

#### Addressing Modes (cont'd)

Base: any register except eip

### Intel vs. AT&T Syntax

What's the AT&T representation of mov rax, [rax + rbx \* 4 + 0x1000]?

## Intel vs. AT&T Syntax

```

What's the AT&T representation of mov rax, [rax + rbx * 4 + 0x1000]?

```

Answer: mov 0x1000(%rax, %rbx, 4), %rax

So which syntax would you like to use?

## Writing Assembly with GNU AS

GNU AS (GNU Assembler) uses the AT&T syntax by default. To use the Intel syntax, you should use a special directive .intel\_syntax noprefix.

#### Example

```

.intel_syntax noprefix

mov rax, [rbx]

```

#### **Pointer Directives**

```

mov [rsi], al ; ok (compiles) mov [rsi], 1 ; error

```

Error: ambiguous operand size for 'mov'

#### **Pointer Directives**

```

mov [rsi], al ; ok (compiles) mov [rsi], 1 ; error

```

Error: ambiguous operand size for 'mov'

#### Because it could be any of the followings

- mov BYTE PTR [rsi], 1

- mov WORD PTR [rsi], 1

- mov DWORD PTR [rsi], 1

- mov QWORD PTR [rsi], 1

#### **Examples: Moving Data Around**

- mov eax, ebx

- mov al, bl

- mov [rax], rbx

- mov rcx, [rbx]

- mov rcx, [rax + rbx \* 4]

- mov al, BYTE PTR [rsi]

- mov rax, 42

- mov DWORD PTR [rax], 42

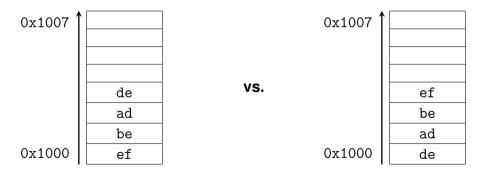

# **Storing a DWORD in Memory**

mov DWORD PTR [rax], Oxdeadbeef

(assume that rax = 0x1000)

# **Storing a DWORD in Memory**

mov DWORD PTR [rax], Oxdeadbeef (assume that rax = 0x1000)

#### **Endianness**

The order in which a sequence of bytes are stored in memory.

- Big endian: The MSB goes to the lowest address.

- Little endian: The LSB goes to the lowest address.

x86 uses Little Endian

#### **Load Effective Address**

- lea rax, [rbx]

- lea rax, [rbp 0x8]

Same as '&' in C

#### What's the Difference?

mov rax, [rbp + 0x10] vs. lea rax, [rbp + 0x10]

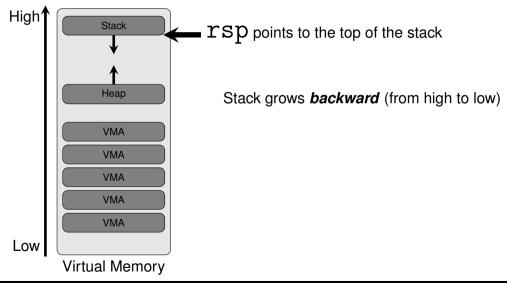

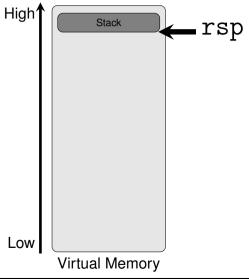

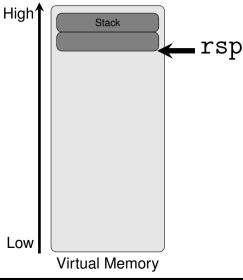

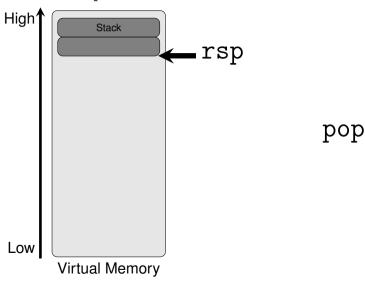

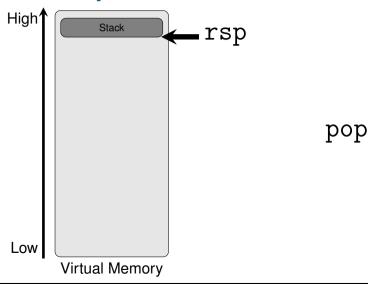

#### **Stack Memory**

Stack stores data in a LIFO (Last-In-First-Out) fashion. When a function is invoked, a new **stack frame** is allocated at the top of the stack memory.

#### **Stack Operations**

push

push

## Stack Push/Pop

```

(On x86): push x = sub esp, 4; mov [esp], x

(On x64): push x = sub rsp, 8; mov [rsp], x

(On x86): pop x = mov x, [esp]; add esp, 4

(On x64): pop x = mov x, [rsp]; add rsp, 8

```

## Stack Enter/Leave (x64)

#### **Function Call**

```

.intel_syntax noprefix

.intel_syntax noprefix

call foo

push nextret

jmp foo

nextret:

nextret:

nop

nop

nop

nop

nop

nop

nop

foo:

nop

foo:

nop

nop

nop

nop

nop

nop

nop

nop

```

#### **Function Return**

ret pop rip

### **Arithmetic and Logical Operations**

- add rax, [rbx]

- sub rsp, 0x40

- inc rcx

- dec rcx

- and [rax + rcx], rbx

- or rdx, rbx

- xor rdx, rbx

- shl rax, 1

- ...

#### **Control Flows**

C has a high-level control structures, such as:

```

if ( x ) { /* A */ }

else { /* B */ }

while ( x ) { }

for ( i = 0; i < n; i++ ) { }</pre>

```

Can we represent these in assembly?

## **Control Flows in Assembly (1)**

There are only "if" and "goto" (no "else").

```

if ( x ) { /* A */ } else { /* B */ }

```

```

if (!x) goto F;

/* A */

goto E;

F:

/* B */

E:

```

## **Control Flows in Assembly (2)**

There are only "if" and "goto" (no "else").

```

while ( x ) { /* body */ } \rightarrow

```

```

WHILE:

if ( !x ) goto DONE;

/* body */

goto WHILE;

DONE:

```

## **Control Flows in Assembly (3)**

There are only "if" and "goto" (no "else").

```

for ( i = 0; i < n; i++ ) { \rightarrow }

```

```

i = 0;

LOOP:

if ( i >= n ) goto DONE;

/* body */

i++;

goto LOOP;

DONE:

```

## **Control Flows in Assembly (Example)**

## **Control Flows in Assembly (Example)**

```

if (!x) goto F;

/* A */

goto E;

F:

/* B */

E:

cmp x, 0

jne F

; A

jmp E

F:

; B

E:

```

Where do we store the result of comparison (cmp)?

## **EFLAGS: Storing the Processor State**

- EFLAGS is a status register used in x86, which is essentially a collection of status flag bits.

- There are approximately 20 different flag bits used in x86, but we are mainly interested in 6 condition flags:

- OF: Overflow flag

- SF: Sign flag

- ZF: Zero flag

- AF: Auxiliary carry flag

- PF: Parity flag

- CF: Carry flag

## **Almost Every x86 Instruction Affects EFLAGS**

add rax, rbx

| rax | 1                     |

|-----|-----------------------|

| rbx | -2 (0xfffffffffffffe) |

| SF  | 0                     |

|     | -1 (Oxffffffffffffff) |

|-----|-----------------------|

| rbx | -2 (0xfffffffffffffe) |

| SF  | 1                     |

and rbx, 0

| rax | -1 (Oxffffffffffffff) |

|-----|-----------------------|

| rbx | 0                     |

| SF  | 0                     |

| ZF  | 1                     |

## cmp Only Affects EFLAGS

cmp is the same as sub, except that it only affects EFLAGS, but not the destination operand. For example, cmp rax, rbx will not change the rax register.

#### **Conditional Branch Instructions**

| Instruction <sup>1</sup> | Condition                       | Description                 |

|--------------------------|---------------------------------|-----------------------------|

| ja                       | CF = 0 and $ZF = 0$             | Jump if above               |

| jb                       | CF = 1                          | Jump if below               |

| je                       | ZF = 1                          | Jump if equal               |

| jl                       | $\mathtt{SF}  eq \mathtt{OF}$   | Jump if less                |

| jle                      | $ZF = 1 \text{ or } SF \neq 0F$ | Jump if less or equal       |

| jz                       | ZF = 1                          | Jump if zero (❶ same as je) |

| (many more)              |                                 |                             |

<sup>&</sup>lt;sup>1</sup>Assume that a comparison instruction precedes the branch instruction.

### Examining the ja Case

#### Example code.

- cmp is the same as sub except that it only updates EFLAGS.

- CF = 0 implies that rax rbx did not produce any carry.

- ZF = 0 implies that the result of subtraction is not zero. Hence,  $rax \neq rbx$ .

- From both the conditions, we can say that rax > rbx.

### **Summary So Far**

- · We learned how to move around data.

- mov, lea, push, pop, etc.

- We learned how to perform arithmetic and logical operations.

- add, sub, and, or, etc.

- We also learned how to control program flows.

- cmp, jmp, ja, jz, etc.

Already Turing complete!

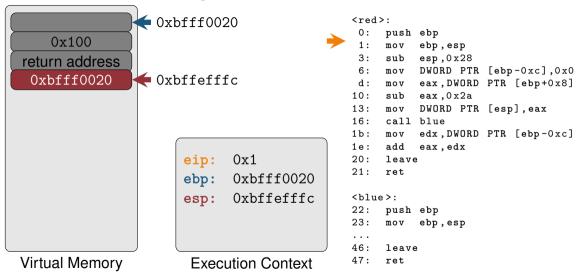

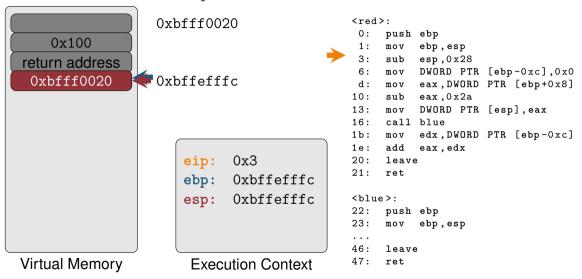

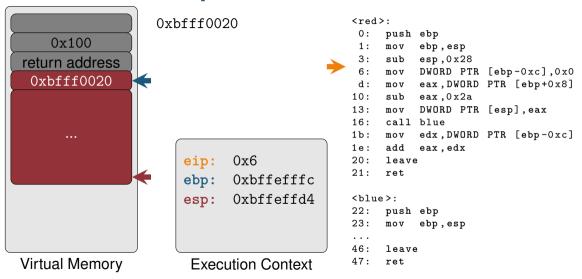

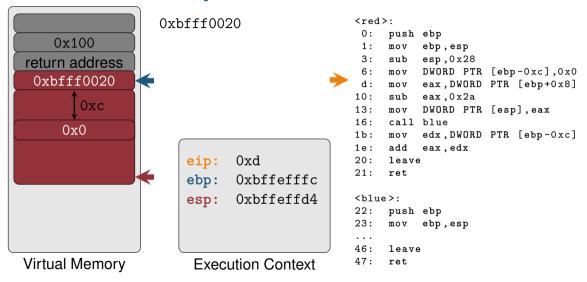

## **x86 Execution Model**

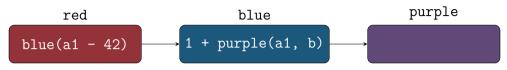

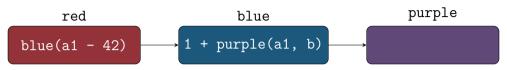

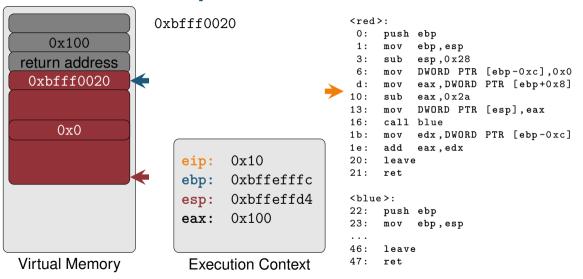

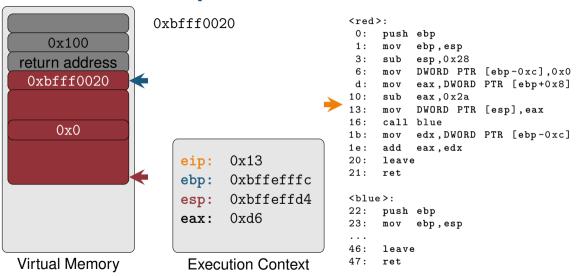

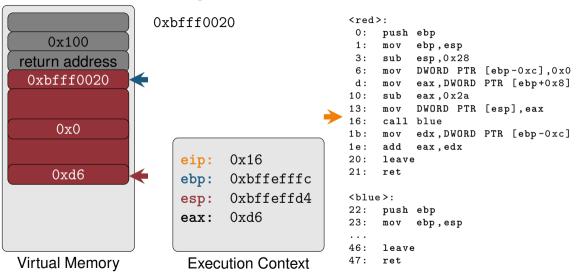

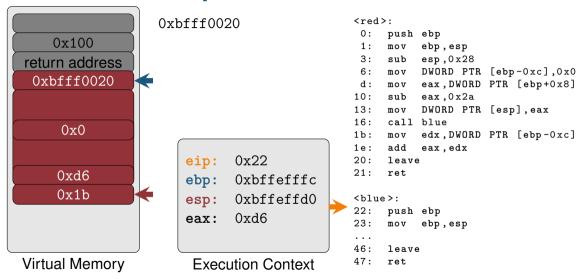

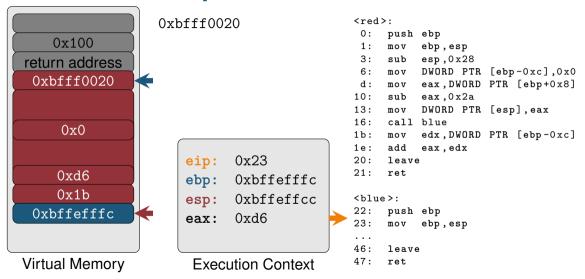

### **Our Example**

```

int purple(int a1, int a2)

return 2 + a1 - a2;

int blue(int a1)

return 1 + purple(a1, b);

int red(int a1)

return blue(a1 - 42);

```

#### Questions

- How do we pass function parameters?

- When a function returns, how do we restore the register values of the caller.

- Where do we store local variables?

#### Questions

- · How do we pass function parameters?

- When a function returns, how do we restore the register values of the caller.

- Where do we store local variables?

We can easily get the answer by compiling the example program and disassembling the resulting binary.

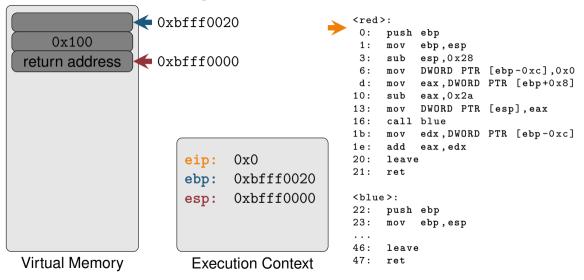

## Disassembled Code (x86)

```

<red>:

32:

mov

DWORD PTR [esp+0x4], eax

36:

eax, DWORD PTR [ebp+0x8]

0:

push

ebp

mov

1:

mov

ebp, esp

39:

DWORD PTR [esp], eax

mov

3:

3c:

sub

esp.0x28

call

purple

6.

mov

DWORD PTR [ebp-0xc],0x0

41:

mov

edx, DWORD PTR [ebp-0xc]

d:

mov

eax, DWORD PTR [ebp+0x8]

44:

add

eax.edx

10:

46:

sub

eax.0x2a

leave

DWORD PTR [esp].eax

13:

mov

47:

ret

16:

call

blue

1b:

edx, DWORD PTR [ebp-0xc]

mov

<purple>:

1e:

add

eax, edx

48:

push

ebp

20:

49:

leave

mov

ebp, esp

21:

4h·

sub

esp.0x10

ret

4e:

mov

DWORD PTR [ebp-0x4],0x2

<blue>:

55:

eax, DWORD PTR [ebp+0x8]

m o v

22:

push

ebp

58:

mov

edx.DWORD PTR [ebp-0x4]

23:

mov

ebp, esp

5b:

add

eax.edx

25:

sub

esp,0x28

5d:

sub

eax, DWORD PTR [ebp+0xc]

28:

DWORD PTR [ebp-0xc].0x1

60:

leave

mov

2f ·

m o v

eax, DWORD PTR [ebp-0xc]

61:

ret

```

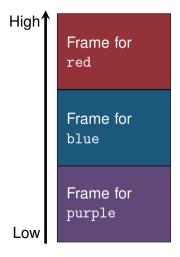

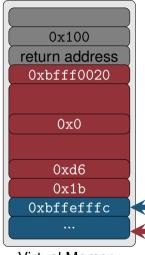

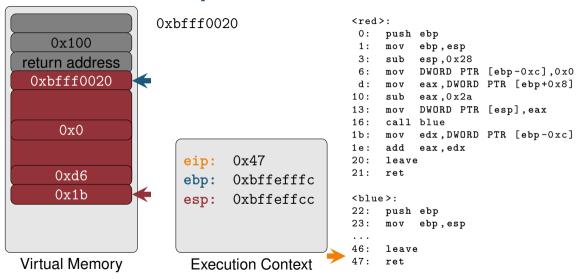

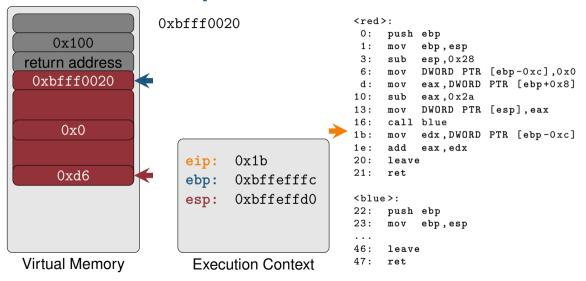

#### **Stack Frames**

Virtual Memory

```

0xbfff0020

eip:

0x46

ebp:

Oxbffeffcc

Oxbffeffac

esp:

Execution Context

```

```

<red>.

push ebp

mov

ebp, esp

esp.0x28

sub

DWORD PTR [ebp-0xc],0x0

mov

eax, DWORD PTR [ebp+0x8]

d:

mov

10:

eax,0x2a

sub

13:

DWORD PTR [esp], eax

mov

16.

call

h111e

1b:

edx, DWORD PTR [ebp-0xc]

mov

1e:

add

eax.edx

20:

leave

21:

ret

<blue>:

22:

push ebp

23:

ebp, esp

mov

mov esp, ebp

46:

leave

pop ebp

47:

ret

```

# **Question?**

#### **Exercise**

- 1. Write any sort function in x86 (or x86-64) assembly, and create an object file.

- 2. Write a C function that tests the sort function. Link with the object file and run your test.